z/VM Version 7 Release 2

Enterprise Systems Architecture/ Extended Configuration Principles of Operation

#### Note:

Before you use this information and the product it supports, read the information in <u>"Notices" on page 57</u>.

This edition applies to Version 7.2 of IBM z/VM (product number 5741-A09) and to all subsequent releases and modifications until otherwise indicated in new editions.

Last updated: 2020-09-08

#### <sup>©</sup> Copyright International Business Machines Corporation 1991, 2020.

US Government Users Restricted Rights – Use, duplication or disclosure restricted by GSA ADP Schedule Contract with IBM Corp.

# Contents

| Figures                                                                           | vii |

|-----------------------------------------------------------------------------------|-----|

| Tables                                                                            | ix  |

| About This Document                                                               | xi  |

| Intended Audience                                                                 | xi  |

| Conventions                                                                       | xi  |

| Where to Find More Information                                                    | xii |

| Links to Other Documents and Websites                                             |     |

| How to Send Your Comments to IBM                                                  |     |

| Summary of Changes for z/VM ESA/Extended Configuration Principles of<br>Operation |     |

| SC24-6285-01, z/VM 7.2 (September 2020)                                           |     |

| SC24-6285-00, z/VM 7.1 (September 2020)                                           |     |

| SC24-6265-00, 2/VM 7.1 (September 2016)<br>SC24-6192-01, z/VM 6.4 (August 2017)   |     |

| 5C24-0192-01, 2/ 11 0.4 (August 2017)                                             | XV  |

| Chapter 1. Introduction                                                           | 1   |

| Highlights of ESA/XC                                                              |     |

| The ESA/390 Base                                                                  |     |

| System Program                                                                    |     |

| Compatibility                                                                     |     |

| Compatibility among ESA/XC Implementations                                        |     |

| Compatibility among ESA/XC, ESA/390, ESA/370, 370-XA and System/370               |     |

| Relationship to z/Architecture                                                    |     |

|                                                                                   | _   |

| Chapter 2. Organization                                                           |     |

| Main Storage                                                                      |     |

| Central Processing Unit                                                           |     |

| Access Registers                                                                  |     |

| Host Access List                                                                  |     |

| Host Program                                                                      |     |

| Chapter 3. Storage                                                                | 7   |

| Storage Addressing                                                                |     |

| Absolute-Storage Address Spaces                                                   |     |

| Private and Shareable Address Spaces                                              |     |

| Identification of Address Spaces                                                  |     |

| Address Types and Formats                                                         |     |

| Address Types and Formats                                                         |     |

| Protection                                                                        |     |

| Key-Controlled Protection                                                         |     |

| Host Access-List-Controlled Protection                                            |     |

| Host Page Protection                                                              |     |

| Low-Address Protection                                                            |     |

| Suppression on Protection                                                         |     |

| Prefixing                                                                         |     |

| Dynamic Address Translation                                                       |     |

| Translation Control.                                                              |     |

|                                                                                   |     |

| <b>—</b>                                                     |    |

|--------------------------------------------------------------|----|

| Translation Modes                                            |    |

| Address Summary                                              |    |

| Addresses Translated                                         |    |

| Handling of Addresses                                        |    |

| Assigned Storage Locations                                   |    |

| Chapter 4. Control                                           | 17 |

| Program-Status Word                                          |    |

| Program-Status-Word Format                                   |    |

| Control Registers                                            |    |

| Tracing                                                      |    |

| Program-Event Recording                                      |    |

| Timing                                                       |    |

| Time-of-Day Clock                                            |    |

| Externally Initiated Functions.                              |    |

| Resets                                                       |    |

|                                                              |    |

| Chapter 5. Program Execution                                 |    |

| Authorization Mechanisms                                     |    |

| Extraction-Authority Control                                 |    |

| Access-Register Mechanisms                                   |    |

| PC-Number Translation                                        |    |

| Home Address Space                                           | 21 |

| Access-Register Introduction                                 |    |

| Summary                                                      | 22 |

| Access-Register Functions                                    | 22 |

| Host Access-Register Translation                             |    |

| Host-Access-Register-Translation Control                     |    |

| Access Registers                                             |    |

| Host-Access-Register-Translation Structures                  |    |

| Host-Access-Register-Translation Process                     |    |

| Linkage Stack                                                |    |

| Sequence of Storage References                               |    |

| Chapter 6. Interruptions                                     | 33 |

| Interruption Action                                          |    |

| Exceptions Associated with the PSW.                          |    |

| Program Interruption                                         |    |

| Program-Interruption Conditions                              |    |

| Multiple Program-Interruption Conditions                     |    |

|                                                              |    |

| Chapter 7. Instructions                                      |    |

| ESA/390 Instructions Not Provided                            |    |

| Modified ESA/390 Instructions                                |    |

| DIAGNOSE                                                     |    |

| INSERT ADDRESS SPACE CONTROL                                 | 40 |

| INSERT STORAGE KEY EXTENDED                                  | 40 |

| INVALIDATE PAGE TABLE ENTRY                                  | 40 |

| LOAD ADDRESS EXTENDED                                        | 40 |

| LOAD PSW                                                     |    |

| LOAD USING REAL ADDRESS                                      |    |

| PURGE ALB                                                    |    |

| PURGE TLB                                                    |    |

| RESET REFERENCE BIT EXTENDED                                 |    |

| RESUME PROGRAM                                               |    |

| SET ADDRESS SPACE CONTROL and SET ADDRESS SPACE CONTROL FAST |    |

| SET STORAGE KEY EXTENDED                                     |    |

| SET SYSTEM MASK                                                      | 43 |

|----------------------------------------------------------------------|----|

| SIGNAL PROCESSOR                                                     | 43 |

| STORE THEN OR SYSTEM MASK                                            | 43 |

| STORE USING REAL ADDRESS                                             |    |

| TEST ACCESS                                                          | 43 |

| TEST BLOCK                                                           | 45 |

| TEST PROTECTION                                                      |    |

| TRACE                                                                |    |

| TRAP                                                                 |    |

| Chapter 8. Machine-Check Handling                                    |    |

| Handling of Machine Checks                                           |    |

| Validation                                                           |    |

| Machine-Check Extended Interruption Information                      |    |

| Failing-Storage Address and ASIT                                     |    |

| Chapter 9. Input/Output                                              |    |

| Handling of Addresses for I/O                                        |    |

| Appendix A. Comparison between ESA/390 and ESA/XC                    |    |

| New Facilities in ESA/XC                                             |    |

| DAT-Off Access-Register Addressing                                   |    |

| Multiple Absolute-Storage Address Spaces                             |    |

| Address-Space Sharing                                                |    |

| Comparison of Facilities                                             |    |

| Summary of Changes<br>Changes in Instructions Provided               |    |

| Comparison of PSW Formats                                            |    |

| Comparison of PSW Formats<br>Changes in Control-Register Assignments |    |

| Changes in Assigned Storage Locations                                |    |

| Changes in Exceptions                                                |    |

| Changes to Insert Address Space Control                              |    |

| Changes to Resume Program                                            |    |

| Changes to Set Address Space Control (SASC) and SASC Fast            |    |

| Changes to Set System Mask                                           |    |

| Changes to Test Access                                               |    |

| Changes to Trap                                                      |    |

| Notices                                                              |    |

| Programming Interface Information                                    |    |

| Trademarks                                                           |    |

| Terms and Conditions for Product Documentation                       |    |

| IBM Online Privacy Statement                                         | 59 |

| Bibliography                                                         |    |

| Where to Get z/VM Information                                        |    |

| z/VM Base Library                                                    |    |

| z/VM Facilities and Features                                         |    |

| Prerequisite Products                                                |    |

| Other Publications                                                   |    |

| Index                                                                |    |

# Figures

| 1. Handling of Addresses (Part 1 of 2)                                                 | .14  |

|----------------------------------------------------------------------------------------|------|

|                                                                                        | 4 5  |

| 2. Handling of Addresses (Part 2 of 2)                                                 | .15  |

| 3. PSW Format                                                                          | .17  |

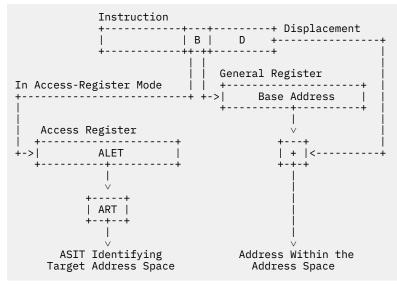

| 4. Use of Access Registers                                                             | .23  |

| 5. Priority of Access Exceptions                                                       | .37  |

| 6. Priority of Execution: SET ADDRESS SPACE CONTROL and SET ADDRESS SPACE CONTROL FAST | .42  |

| 7. Priority of Execution: TEST ACCESS                                                  | . 45 |

# **Tables**

| 1. Translation Modes                                      | 12 |

|-----------------------------------------------------------|----|

| 2. Availability of ESA/390 Facilities in ESA/XC           | 52 |

| 3. ESA/390 Instructions Not Provided in ESA/XC            | 53 |

| 4. ESA/390 Control-Register Fields Not Assigned in ESA/XC | 54 |

| 5. Changes in Assigned Storage Locations                  | 54 |

| 6. ESA/390 Exceptions Not Recognized                      | 55 |

# **About This Document**

This document provides a detailed description of the IBM<sup>®</sup> Enterprise Systems Architecture/Extended Configuration (ESA/XC) virtual-machine architecture, as provided by z/VM<sup>®</sup>. It describes the way an ESA/XC virtual machine operates as it appears to an assembler language programmer. Because ESA/XC is based on and is closely related to Enterprise Systems Architecture/390<sup>®</sup> (ESA/390), this document defines ESA/XC by indicating the ways in which it is the same as, or different from, ESA/390.

The following elements of the ESA/XC architecture are covered in this document:

- Overall organization

- The structure of storage and address spaces

- Control facilities

- Program execution

- Interruptions

- The operation of instructions

- Input/output facilities

# **Intended Audience**

This document is intended for programmers who write or debug programs that run in ESA/XC virtual machines.

You should have a basic familiarity with the ESA/390 architecture, or alternatively, the Enterprise Systems Architecture/370 (ESA/370) or System/370 Extended Architecture (370-XA) upon which ESA/390 is based. These architectures are described in:

- IBM Enterprise Systems Architecture/390 Principles of Operation, SA22-7201

- IBM Enterprise Systems Architecture/370 Principles of Operation, SA22-7200

- IBM System/370 Extended Architecture Principles of Operation, SA22-7085

You should also know IBM basic assembler language and have experience with z/VM programming concepts and techniques.

# Conventions

This document is intended to be used in conjunction with the definition of ESA/390 provided in *IBM Enterprise Systems Architecture/390 Principles of Operation*. Where possible, information is presented in this document using the same style and general organization as *IBM Enterprise Systems Architecture/390 Principles of Operation*. To assist in locating corresponding information in the two documents, the following table shows the relationship of the chapters of this document to the chapters in *IBM Enterprise Systems Architecture/390 Principles of Operation*.

| Chapter in this document                           | Corresponding chapter(s) in <i>IBM Enterprise Systems Architecture/390</i><br><i>Principles of Operation</i> , SA22-7201-08 |

|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Chapter 1, "Introduction," on page $\underline{1}$ | Chapter 1, Introduction                                                                                                     |

| Chapter 2, "Organization," on page 5               | Chapter 2, Organization                                                                                                     |

| Chapter 3, "Storage," on page 7                    | Chapter 3, Storage                                                                                                          |

| Corresponding chapter(s) in <i>IBM Enterprise Systems Architecture/390</i><br><i>Principles of Operation</i> , SA22-7201-08                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 4, Control                                                                                                                                                                                                                                                       |

| Chapter 5, Program Execution                                                                                                                                                                                                                                             |

| Chapter 6, Interruptions                                                                                                                                                                                                                                                 |

| Chapter 7, General Instructions Chapter 8, Decimal Instructions Chapter<br>9, Floating-Point Overview and Support Instructions Chapter 10, Control<br>Instructions Chapter 18, Hexadecimal-Floating-Point Instructions<br>Chapter 19, Binary-Floating-Point Instructions |

| Chapter 11, Machine-Check Handling                                                                                                                                                                                                                                       |

| Chapter 13, I/O Overview Chapter 14, I/O Instructions Chapter 15, Basic I/O Functions Chapter 16, I/O Interruptions Chapter 17, I/O Support Functions                                                                                                                    |

|                                                                                                                                                                                                                                                                          |

Enterprise Systems Architecture/390 Principles of Operation.

# Where to Find More Information

Besides the document *IBM Enterprise Systems Architecture/390 Principles of Operation*, the following documents in the z/VM library may be useful in understanding ESA/XC:

- z/VM: CP Programming Services

- z/VM: CMS Application Development Guide

- z/VM: CMS Callable Services Reference

- z/VM: CMS Application Development Guide for Assembler

- z/VM: CMS Macros and Functions Reference

For the complete list of documents in the z/VM library, see the "Bibliography" on page 61.

### Links to Other Documents and Websites

The PDF version of this document contains links to other documents and websites. A link from this document to another document works only when both documents are in the same directory or database, and a link to a website works only if you have access to the Internet. A document link is to a specific edition. If a new edition of a linked document has been published since the publication of this document, the linked document might not be the latest edition.

# How to Send Your Comments to IBM

We appreciate your input on this publication. Feel free to comment on the clarity, accuracy, and completeness of the information or give us any other feedback that you might have.

To send us your comments, go to <u>z/VM Reader's Comment Form (www.ibm.com/systems/</u> campaignmail/z/zvm/zvm-comments) and complete the form.

#### If You Have a Technical Problem

Do not use the feedback method. Instead, do one of the following:

- Contact your IBM<sup>®</sup> service representative.

- Contact IBM technical support.

- See IBM: z/VM Support Resources (www.ibm.com/vm/service).

- Go to IBM Support Portal (www.ibm.com/support/entry/portal/Overview).

xiv z/VM: z/VM 7.2 Enterprise Systems Architecture/Extended Configuration Principles of Operation

# Summary of Changes for z/VM ESA/Extended Configuration Principles of Operation

This information includes terminology, maintenance, and editorial changes. Technical changes or additions to the text and illustrations for the current edition are indicated by a vertical line to the left of the change.

# SC24-6285-01, z/VM 7.2 (September 2020)

This edition supports the general availability of z/VM<sup>®</sup> 7.2.

# SC24-6285-00, z/VM 7.1 (September 2018)

This edition supports the general availability of z/VM 7.1.

# SC24-6192-01, z/VM 6.4 (August 2017)

This edition includes changes to support product changes provided or announced after the general availability of z/VM 6.4.

$\textbf{xvi} \hspace{0.1 cm} z/VM: z/VM \hspace{0.1 cm} 7.2 \hspace{0.1 cm} \text{Enterprise Systems Architecture/Extended Configuration Principles of Operation}$

# **Chapter 1. Introduction**

This document describes, for reference purposes, the operation of virtual machines that execute in the ESA/XC virtual-machine architecture as provided by z/VM. It is organized as a supplement to the definition of the ESA/390 architecture described in *IBM Enterprise Systems Architecture/390 Principles of Operation*.

If a particular element of the architecture (instruction, operation, program exception, etc.) is described in this document, then the definition contained in this document supersedes the definition in *IBM Enterprise Systems Architecture/390 Principles of Operation*. If there is no discussion of a particular element of the architecture in this document, then the definition contained in *IBM Enterprise Systems Architecture/390 Principles of Operation*. If there is no discussion of a particular element of the architecture in this document, then the definition contained in *IBM Enterprise Systems Architecture/390 Principles of Operation*. If there is no discussion of a particular element of the architecture in this document, then the definition contained in *IBM Enterprise Systems Architecture/390 Principles of Operation*.

ESA/XC comprises the architectural facilities available to the program that is executing in the virtual machine. ESA/XC virtual machines operate under the control of the z/VM Control Program (CP), a host program that runs in the ESA/390 processor complex and manages the structures that establish the virtual machines. The details of these structures do not directly affect the program in the virtual machine and are therefore not described in this document.

# Highlights of ESA/XC

The ESA/XC virtual-machine architecture is a derivative of Enterprise Systems Architecture/390 (ESA/ 390) that is designed for the DAT-off virtual-machine environment. This virtual-machine architecture includes most of the facilities of ESA/390 and offers major new capabilities.

ESA/XC was designed with special emphasis on the requirements of the interactive and service-virtualmachine environments of z/VM. In these environments, the supervisor running in the virtual machine is not an elaborate control program, but rather an application-program monitor. Consistent with such a virtual-machine supervisor, ESA/XC allows application programs to benefit from architectural extensions provided by ESA/390 without requiring the virtual-machine supervisor to perform complex management functions. Instead, the host bears the responsibility for the support and management of the real-machine facilities.

ESA/XC is also designed to take into account the multiple-virtual-machine environment of z/VM. By giving the responsibility for support and control of the architecture to the host, the scope of access that can be allowed using the architecture can be extended in a controlled and secure manner across multiple virtual machines. Previously, the scope of access possible using architectural facilities was necessarily limited to a single virtual machine.

When compared to ESA/390, ESA/XC offers the following extensions:

- DAT-off access-register addressing makes the access-register-addressing facility of ESA/370 and ESA/390 available to z/VM applications. The facility can be used by a virtual machine to access its own address spaces as well as the address spaces of other virtual machines, subject to appropriate authorization.

- *Multiple absolute-storage address spaces* significantly extend the amount of storage available to z/VM applications. Previously, the storage available to an application was limited to a single 2 gigabyte absolute-storage address space. With this facility, an application can have multiple 2 gigabyte data-only spaces in addition to the instruction space, providing greatly increased application storage.

- Address-space sharing provides a basis for high-performance data sharing within a z/VM system. A virtual machine can authorize other virtual machines to access, by means of access-register addressing, any of its address spaces (the instruction address space, or any data-only address spaces). The shared access can be subsequently revoked when the shared access is no longer appropriate.

## The ESA/390 Base

ESA/XC includes, as its base, most of the facilities available to ESA/390 virtual machines. However, some of the facilities available in ESA/390 are not provided in ESA/XC. This section summarizes these differences.

The most significant difference between ESA/390 and ESA/XC is that in ESA/XC, guest dynamic address translation (DAT) is not provided. Consequently, in ESA/XC:

- Guest virtual-storage address spaces are not provided. Therefore, there are no guest segment tables or page tables, nor is there a guest translation-lookaside buffer.

- The dual-address-space facility is not provided. Therefore, the EXTRACT PRIMARY ASN, EXTRACT SECONDARY ASN, INSERT VIRTUAL STORAGE KEY, LOAD ADDRESS SPACE PARAMETERS, MOVE TO PRIMARY, MOVE TO SECONDARY, PROGRAM CALL, PROGRAM TRANSFER and SET SECONDARY ASN instructions are not provided. The ASN-translation and PC-number translation processes are never performed, and consequently, there are no guest ASN first tables, ASN second tables, linkage tables and entry tables. There are no guest primary and secondary spaces, nor is the secondary-space mode provided.

- Guest access-register translation is not provided. Therefore, there are no guest access lists, nor dispatchable-unit-control tables. A guest ART-lookaside buffer is not provided. (Host access-register translation is provided as a comparable replacement for guest access-register translation.)

- The linkage stack is not provided, nor are the instructions BRANCH AND STACK, EXTRACT STACKED REGISTERS, EXTRACT STACKED STATE, MODIFY STACKED STATE, and PROGRAM RETURN.

- The home address space is not provided, nor is the home-space mode.

- The private-space facility is not provided.

In addition, ESA/XC does not provide the instructions LOAD REAL ADDRESS, SET CLOCK, and START INTERPRETIVE EXECUTION.

In contrast, the facilities previously mentioned as well as extensions to them are available to the host program. Since this document provides in detail only the architecture of the virtual-machine environment, reference is made to host facilities only as needed to clearly describe the programming environment provided by the virtual machine.

Except for facilities specifically identified in this document as not provided, ESA/XC includes all facilities that are defined in ESA/390.

## **System Program**

ESA/XC is typically used with a virtual-machine supervisor program, such as CMS, that cooperates with the host to provide application-level service interfaces for application programs executed within a single virtual machine. An ESA/XC virtual machine operates under the control of the z/VM Control Program (CP) running in the ESA/390 processor complex. The z/VM Control Program acts as the host program, managing the execution of virtual machines and providing system-level services to the virtual machines.

# Compatibility

### **Compatibility among ESA/XC Implementations**

ESA/XC virtual machines can be provided when z/VM is operating on different real-processor implementations, and may be provided by different implementations of the host program. These different implementations of ESA/XC are logically compatible. Specifically, any program written for ESA/XC gives identical results on any ESA/XC implementation, provided that the program:

1. Is not time dependent.

- 2. Does not depend on system facilities (such as storage capacity, I/O equipment, optional machine facilities or optional or release-dependent host-program facilities) being present when the facilities are not included in the configuration or are not provided by the host program implementation.

- 3. Does not depend on system facilities being absent when the facilities are included in the configuration. For example, the program must not depend on interruptions caused by the use of operation codes or command codes that are not installed in some real-processor models, or not provided by some host program versions. Also, it must not use or depend on fields associated with uninstalled facilities. For example, data should not be placed in an area used by another model for fixed-logout information. Similarly, the program must not use or depend on unassigned fields in machine formats (control registers, instruction formats, etc.) that are not explicitly made available for program use.

- 4. Does not depend on results or functions that are defined to be unpredictable or model-dependent or are identified as undefined. This includes the requirement that the program should not depend on the assignment of device numbers and CPU addresses.

- 5. Does not depend on results or functions that are defined in the functional-characteristics publication for a particular real-processor model to be deviations from the ESA/390 architecture where those results or functions of ESA/390 are applicable in ESA/XC.

- 6. Takes into account any changes made to the architecture that are identified as affecting compatibility.

## Compatibility among ESA/XC, ESA/390, ESA/370, 370-XA and System/370

#### Supervisor-State Compatibility

A supervisor-state program written for 370-XA, ESA/370 or ESA/390 that uses the dynamic-address-translation (DAT) facility cannot be transferred to an ESA/XC virtual machine because ESA/XC does not provide DAT.

A supervisor-state program written for 370-XA, ESA/370 or ESA/390 that does not use the DAT facilities can be transferred to an ESA/XC virtual machine, provided that the control program:

- 1. Complies with the limitations described in the section <u>"Compatibility among ESA/XC</u> <u>Implementations" on page 2</u> in this chapter.

- 2. Does not depend for correct operation on receiving a special-operation exception when a control instruction that in ESA/390 requires DAT to be on for successful execution is attempted in an ESA/XC virtual machine.

- 3. Does not use the following instructions:

- LOAD ADDRESS SPACE PARAMETERS

- LOAD REAL ADDRESS

- SET CLOCK

- START INTERPRETIVE EXECUTION

Supervisor-state programs written for System/370\*, regardless of whether the DAT facility is used, cannot be directly transferred to virtual machines operating as defined by ESA/XC. This is because the basic-control mode is not present and the facilities for I/O are changed in the ESA/390 base of ESA/XC. (See Appendixes D, E and F of *IBM Enterprise Systems Architecture/390 Principles of Operation* for a detailed comparison among ESA/390, ESA/370, 370-XA and System/370. See <u>Appendix A, "Comparison between ESA/390 and ESA/XC," on page 51</u> of this publication for a detailed comparison between ESA/XC.

#### **Problem-State Compatibility**

A high degree of compatibility exists at the problem-state level in transferring from ESA/390, ESA/370, 370-XA or System/370 to ESA/XC operation.

A problem-state program written for ESA/390, ESA/370, 370-XA or System/370 operates with ESA/XC provided that the program:

- 1. Complies with the limitations described in the section <u>"Compatibility among ESA/XC</u> Implementations" on page 2 in this chapter.

- 2. Is not dependent on host or virtual-machine supervisor facilities that are unavailable on the system.

- 3. Takes into account other changes made to the System/370 architectural definition that affect compatibility between System/370 and the 370-XA base of ESA/390. These changes are described in Appendix F of *IBM Enterprise Systems Architecture/390 Principles of Operation*.

## **Relationship to z/Architecture**

z/Architecture<sup>™</sup> extends ESA/390 by providing 64-bit addressing registers and arithmetic operations. z/VM runs only in z/Architecture (64-bit) mode. However, ESA/XC remains a derivative of ESA/390. ESA/XC virtual machines are supported, but are limited to 31-bit addressing and 32-bit registers and arithmetic operations. An ESA/XC virtual machine cannot operate in 64-bit mode.

# **Chapter 2. Organization**

The basic organization of an ESA/XC virtual machine follows the definition of system organization provided in Chapter 2 of *ESA/390 Principles of Operation*. In addition, an ESA/XC virtual machine has an extended configuration that is described by the information in this chapter.

An ESA/XC virtual-machine configuration contains all of the basic organizational elements defined for ESA/390 systems: main storage, one or more central processing units (CPUs), operator facilities, a channel subsystem and I/O devices. In addition, an ESA/XC configuration has available additional separate absolute-storage address spaces, up to 15 of which are concurrently addressable as provided by access-register addressing. These 15 absolute-storage address spaces are selected from among a larger set as determined by a table called a host access list.

Certain elements of an ESA/XC virtual-machine configuration are regulated by host controls available to the z/VM installation. For example, the total main storage provided to a virtual machine is regulated by host controls. These host controls are specified in the host (CP) directory entry for the virtual machine.

Contrary to the ESA/390 definition, the main storage of an ESA/XC virtual machine is not necessarily isolated from access by the CPUs of other virtual machines. By using host services, the main storage of one virtual machine can be made directly addressable by the CPUs of another configuration. This shared main storage can be used to provide shared data for a collection of virtual machines executing on a single z/VM system.

## **Main Storage**

As in ESA/390, directly addressable main storage is provided for high-speed processing of data by the CPU and the channel subsystem.

Main storage is allocated in extents known as absolute-storage address spaces, or simply address spaces. When a virtual machine is created by the host, an initial address space is provided for the virtual machine; this address space is known as the host-primary address space. Initially, the host-primary address space is directly addressable only by the CPUs of the associated virtual machine. However, through the use of host services, the host-primary address space may be made directly addressable by the CPUs of other virtual machines.

Optionally, additional absolute-storage address spaces may be added to the virtual configuration by means of host services. These additional address spaces can be established as directly addressable by the CPUs of the associated virtual machine and by the CPUs of other virtual machines as appropriate.

# **Central Processing Unit**

A central processing unit (CPU) of an ESA/XC virtual configuration includes all of the registers provided in ESA/390: the PSW, general registers, floating-point registers, control registers, access registers, the prefix register, and the registers for the clock comparator and CPU timer.

## **Access Registers**

As in ESA/390, ESA/XC provides 16 access registers numbered 0-15. An access register contains an indirect specification of an absolute-storage address space. When the CPU is in a mode called the access-register mode (controlled by a bit in the PSW), an instruction B field used to specify a logical or real address for a storage-operand reference designates an access register. The storage-operand is considered to reside within the absolute-storage address space specified by the access register. For some instructions, an R field is used instead of a B field. Instructions are provided for loading and storing the contents of access registers and for moving the contents of one access register to another.

Each of access registers 1-15 can designate any address space, including the instruction space (the hostprimary address space). Access register 0 always designates the instruction space. When one of the access registers 1-15 is used to designate an address space, the CPU determines which address space is designated by translating the contents of the access register using host-managed tables. When access register 0 is used to designate an address space, the CPU treats the access register as designating the instruction space, and it does not examine the actual contents of the access register. Therefore, the 16 access registers can designate, at any one time, the instruction space and a maximum of 15 other address spaces.

## **Host Access List**

An ESA/XC virtual machine has a host access list that specifies the set of address spaces, in addition to the virtual machine's host-primary address space, that are available to a CPU when it is in the access-register mode. The host access list contains a directory-specified number of host access-list entries, each of which either designates a particular address space or is considered unused.

Through the use of host services, a host access-list entry can be set to designate a particular address space or can be returned to the unused state.

## **Host Program**

An ESA/XC virtual machine operates under the control of the z/VM Control Program (CP); this supervisory program is called the host program, or simply the host. The host runs in z/Architecture mode or the ESA/390 processor complex and manages the execution of virtual machines, possibly of varying architectures. It also provides special service functions in addition to the facilities described by the architecture(s).

The extended addressing capabilities of ESA/XC are under the control of the host, which determines the extent to which a particular ESA/XC virtual machine can use these extended capabilities. Services are provided by which an ESA/XC virtual machine can request that its capabilities be altered. These services include the creation and deletion of additional address spaces and the modification of host access lists. These host services are described in detail in the publication *z/VM: CP Programming Services*.

# **Chapter 3. Storage**

This chapter describes the structure of main storage, including addressing and protection aspects, for an ESA/XC virtual machine. Except as described in this chapter, the handling of storage for an ESA/XC virtual machine follows the definition of storage provided in Chapter 3 of *IBM Enterprise Systems Architecture/390 Principles of Operation*.

**Note:** Because most references to storage for an ESA/XC virtual machine apply to (guest) real storage, the abbreviated term "storage" is often used in place of "real storage". The term "storage" may also be used in place of "main storage" or "absolute storage" when the meaning is clear.

# **Storage Addressing**

The addressable storage of an ESA/XC virtual machine consists of one or more extents of main storage known as absolute-storage address spaces. The storage contained within a single absolute-storage address space is viewed as a long horizontal string of bits, subdivided into bytes as is usual for ESA/390.

# **Absolute-Storage Address Spaces**

An absolute-storage address space is a single extent of main storage that is directly addressable by a CPU or the channel subsystem. An absolute-storage address space consists of a collection of byte locations, and a set of byte addresses assigned to those byte locations.

**Note:** Because all references to address spaces for an ESA/XC virtual machine apply to absolute-storage address space and not to virtual-storage address spaces, the abbreviated term "address space" is often used in place of "absolute-storage address space".

Each byte location in storage is identified by a non-negative integer which is the byte address of the storage location within an absolute-storage address space. Byte locations are assigned addresses starting at 0, and the addresses are always assigned in complete 4K-byte blocks on integral boundaries.

A byte address uniquely identifies a byte within the collection of bytes associated with a specific absolute-storage address space. However, a particular value of a byte address may not identify a unique byte since a particular byte address may be associated with more than one absolute-storage address space.

A virtual machine has at least one absolute-storage address space, known as its host-primary address space. This address space is provided by the host when the virtual machine is created.

A virtual machine may obtain additional absolute-storage address spaces by using the ADRSPACE CREATE host service. These additional absolute-storage address spaces may be subsequently destroyed by using the ADRSPACE DESTROY host service. Subsystem reset will also destroy all absolute-storage address spaces created by the ADRSPACE CREATE service.

In an absolute-storage address space created by means of the ADRSPACE CREATE host service, addresses are assigned in a single contiguous range. However, in the host-primary address space of a virtual machine, there may be multiple discontiguous ranges of assigned addresses.

The number and total size of absolute-storage address spaces permitted for the virtual machine is subject to directory-specified limits.

**Programming Note:** The ADRSPACE CREATE host service is described in the publication <u>z/VM: CP</u> <u>Programming Services</u>. The number and total size of address spaces that the virtual machine can create by means of ADRSPACE CREATE is specified by the XCONFIG ADDRSPACE statement in the CP directory. The size of the virtual machine's host-primary address space is specified by the USER or IDENTITY statement in the CP directory. These three directory statements are described in the publication <u>z/VM: CP</u> *Planning and Administration*.

## **Private and Shareable Address Spaces**

An absolute-storage address space is considered to be either a private address space, or a shareable address space, as follows.

An address space is a private address space if the address space is directly addressable only by the CPUs of a single virtual machine. An address space is a shareable address space if the address space can be directly addressed by the CPUs of more than one virtual machine.

Immediately after an address space is created by the host, the address space is a private address space. Through the use of the ADRSPACE PERMIT host service, a private address space may be transformed into a shareable address space, subject to a directory-specified authorization to share address spaces. Subsequently, through the use of the ADRSPACE ISOLATE host service, a shareable address space can be transformed into a private address space. Subsystem reset will also transform a shareable address space into a private address space.

**Programming Note:** The ADRSPACE PERMIT and ADRSPACE ISOLATE host services are described in the publication *z/VM: CP Programming Services*.

## **Identification of Address Spaces**

As a mechanism for differentiating one address space from another, each address space has associated with it an eight-byte identifying value called an address-space identification token, or ASIT.

The host assigns an ASIT to each address space when the address space is created. The ASIT associated with a particular absolute-storage address space is fixed from the time the address space is created by the host until it is subsequently destroyed.

The host assigns ASITs in such a way that a particular ASIT value will be associated with at most one absolute-storage address space for the scope of the host IPL. That is, once a particular ASIT value has been assigned to an absolute-storage address space, that ASIT value will not be reassigned to another absolute-storage address space within the scope of the same host IPL, even if the absolute-storage address space to which the ASIT value was originally assigned is subsequently destroyed. ASIT values are not guaranteed to be assigned in any particular manner across a host IPL.

The value 00000000000000 hex is never assigned as an ASIT.

The specific format of an ASIT is undefined. In general, a particular ASIT value will have no significance to ESA/XC programs.

# **Address Types and Formats**

### **Address Types**

For purposes of addressing main storage, two basic types of addresses are recognized: absolute and real. The addresses are distinguished on the basis of the transformations that are applied to the address during a storage access. In addition to the two basic address types, additional types are defined which are treated as one or another of the two basic types depending on the instruction and the current mode.

#### **Absolute Address**

An absolute address is the address assigned to a main-storage location within a particular address space. An absolute address is used for access to storage contained in a particular address space without any transformations performed on it.

#### **Host-Primary Absolute Address**

A host-primary absolute address is an absolute address that identifies a location contained within the host-primary address space.

#### **AR-Specified Absolute Address**

An AR-specified absolute address is an absolute address that identifies a location contained within an address space determined by host access-register translation.

#### **Real Address**

A real address identifies a location within a real address space. In ESA/XC, each real address is considered to be one of two types: type-R or type-A. These types determine the way in which the real address is converted into an absolute address. They also determine the applicability of low-address protection and fetch protection to references using the real address.

When a type-R real address is used for access to main storage, it is converted by means of prefixing to an absolute address. Low-address protection is applied to storage references made using a type-R real address subject to the setting of the low-address-protection control in control register 0. Fetch-protection checking is performed for storage references made using a type-R real address subject to the setting of the fetch-protection-override control in control register 0.

When a type-A real address is used for access to main storage, it is treated unchanged as an absolute address; no prefixing is applied. Low-address protection is never applied to a storage references made using a type-A real address, regardless of the setting of the low-address-protection control in control register 0. Fetch-protection checking is always applied to a storage reference made using a type-A real address, regardless of the fetch-protection-override control in control register 0.

The set of byte locations with a single absolute-storage address space sequenced according to their real addresses is referred to as a real address space.

#### **Host-Primary Real Address**

A host-primary real address is a real address that identifies a location contained within the host-primary address space. A host-primary real address is considered to be a type-R real address.

#### **AR-Specified Real Address**

An AR-specified real address is a real address that identifies a location contained within an address space determined by host access-register translation. An AR-specified real address is considered to be a type-R real address when the ALET used is 00000000 hex. An AR-specified real address is considered to be a type-A real address when the ALET used is other than 00000000 hex.

#### **Virtual Addresses**

Since the dynamic-address-translation facility is not provided in ESA/XC, virtual addresses and virtual storage are not available for ESA/XC virtual machines.

#### **Logical Addresses**

Except where otherwise specified, the storage-operand addresses for instructions are logical addresses. Logical addresses are treated as host-primary real addresses when in the primary-space mode, and as AR-specified real addresses when in the access-register mode. Some instructions have storage operand addresses or storage accesses associated with the instruction which do not follow the rules for logical addresses. In all such cases, the instruction definition contains a definition of the type of address.

#### **Instruction Address**

Addresses used to fetch instructions from storage are called instruction addresses. An instruction address is treated as a host-primary real address in all cases. The instruction address in the current PSW and the target address of EXECUTE are instruction addresses.

## Protection

Four protection facilities are provided to protect the contents of main storage from destruction or misuse by programs that contain errors or are unauthorized: key-controlled protection, host access-listcontrolled protection, host page protection, and low-address protection. These protection facilities are applied independently; access to main storage is only permitted when none of the facilities prohibits the access.

Key-controlled protection affords protection against improper storing or against improper storing and fetching, but not against improper fetching alone. The key-controlled-protection mechanism is under the control of the program in the virtual machine.

Host access-list-controlled protection, host page protection, and low-address protection afford protection against improper storing. Host access-list-controlled protection and host page protection are under control of the host and cannot be circumvented by a program in the virtual machine. Low-address protection is under control of the program in the virtual machine.

Guest access-list-controlled protection and page protection as defined in ESA/390 is not available in ESA/XC since the dynamic address translation facility is not provided.

**Programming Note:** In contrast, if the host has applied either host access-list-controlled protection or host page protection to prevent a particular storage or storage-key alteration by the virtual machine, the program in the virtual machine cannot circumvent this protection. This attribute makes host access-list-controlled protection and host page protection appropriate for sharing of storage among virtual machines where protection is required.

Host access-list-controlled protection is particularly useful for sharing of storage among virtual machines because it regulates accesses using an attribute of an individual reference rather than using an attribute of the shared storage itself. This allows some virtual machines to be given authorization to store into the share storage while other, less authorized, virtual machines are prevented from storing.

Low-address protection is not discussed in this note because low-address protection applies only to a virtual machine's references to its own host-primary address space and is therefore not applicable to cross-virtual-machine sharing of storage under z/VM.

### **Key-Controlled Protection**

Key-controlled protection as defined in ESA/390 applies, except for the applicability of the fetch-protection-override control as stated in the following section.

#### **Fetch-Protection-Override Control**

When the fetch-protection-override control (bit 6 of control register 0) is one, fetch protection is ignored for storage references to locations at effective addresses 0-2047 if the storage reference is made with a type-R real address or a logical address that is treated as a type-R real address. Fetch protection checking is always performed for storage references made with a type-A real address or a logical address, regardless of the setting of the fetch-protection-override control.

### **Host Access-List-Controlled Protection**

Host access-list-controlled protection controls store accesses to an address space by means of a readonly or read/write access type maintained in each host access-list entry. The access-type control is not directly accessible to any virtual machine. Host access-list-controlled protection provides protection against unauthorized storing or explicit storage-key alteration.

In the access-register mode, when a host access-list entry is used in the host-access-register-translation part of a reference and the host access-list entry indicates read/write access, both fetch and store accesses are permitted to the address space specified by the host access-list entry. Explicit alteration of storage keys within the address space is also permitted. When the host access-list entry indicates read-only access, fetch accesses to storage or storage keys are permitted, and an attempt to store or to alter explicitly a storage key causes a protection exception to be recognized and the execution of the instruction to be terminated or suppressed.

Host access-list-controlled protection applies to all store accesses or storage-key alterations made by means of a host access-list entry.

The access type permitted by a host access-list entry is established when the host access-list entry is made valid by means of the ALSERV ADD host service. If the host access-list entry designates an address

space owned by another virtual machine, establishing a host access-list entry permitting read/write access is subject to authorization. This authorization is granted by means of the ADRSPACE PERMIT host service by the virtual machine that owns the address space.

**Programming Note:** The ALSERV ADD and ADRSPACE PERMIT host services are described in the publication *z/VM: CP Programming Services*.

## **Host Page Protection**

Host page protection controls store-type references to a 4K-byte block of storage (page) by means of a read-only or read/write authorization associated with each 4K-byte block of storage. The authorization control is not accessible by any virtual machine. Host page protection provides protection against unauthorized storing or storage-key alteration.

When the authorization associated with a 4K-byte block of storage indicates read/write access, both fetching of and storing into the block are permitted, including the explicit alteration of the storage key for the block. When the authorization associated with the block indicates read-only access, only fetching is permitted. When an attempt is made to store into a protected block or alter the storage key for a protected block, a protection exception is recognized and the operation is terminated or suppressed. The contents of the protected location remain unchanged.

Host page protection applies to all store accesses or storage-key alterations made by a virtual machine.

The access authorization associated with a 4K-byte block of storage is established by the host based on the host-defined characteristics of that block of storage.

**Programming Note:** The only 4K-byte blocks of storage established by z/VM as read-only pages are:

- those that correspond to shared read-only (SR) or exclusive read-only (ER) ranges of named saved systems or named saved segments embedded in the host-primary address space.

- those that are mapped by means of the MAPMDISK host service to minidisk blocks on a read-only minidisk. The MAPMDISK host service is described in the publication *z/VM: CP Programming Services*.

All other 4K-byte blocks of storage addressable by the virtual machine are established as read/write pages.

### **Low-Address Protection**

Low-address protection operates as defined in ESA/390, except as stated in the following.

When the low-address-protection control (bit 3 of control register 0) is one, low-address protection applies to storage references to locations at effective addresses 0-511 if the storage references are made with a type-R real address or a logical address that is treated as a type-R real address. Low-address protection does not apply for storage references made with a type-A real address or a logical address of the setting of the low-address-protection control.

### **Suppression on Protection**

If the suppression-on-protection facility is installed, then, during a program interruption due to a protection exception, either a one or a zero is stored in bit position 29 of real locations 144-147. The storing of a one in bit position 29 indicates that:

- The unit of operation or instruction execution during which the exception was recognized was suppressed, except that, if the instruction execution would set the condition code if completed normally, the condition code is unpredictable.

- Bit positions 1-19 of real locations 144-147 contain bits 1-19 of the effective address that caused the exception. The effective address is the address which exists before any transformation by prefixing. Bit positions 30 and 31 of real locations 144-147, and real locations 160, contain information identifying the address space containing the protected address.

Bit 29 being zero indicates that the operation was either suppressed or terminated and that the contents of the remainder of real locations 144-147, and of real location 160, are unpredictable.

No protection-exception conditions necessarily set bit 29 to one.

# Prefixing

Prefixing operates as defined in ESA/390, except as stated in the following.

Prefixing is applied to convert a type-R real address into an absolute address. Prefixing is not applied to convert a type-A real address into an absolute address, but rather the type-A real address is treated unchanged as an absolute address.

# **Dynamic Address Translation**

The dynamic address translation facility provided in ESA/390 is not available in ESA/XC.

Consequently, the following additional DAT-related facilities defined in ESA/390 are also not available in ESA/XC:

- Virtual-storage address spaces

- Address-space numbers (ASNs)

- ASN-translation controls, tables and process

- ASN-authorization controls and process

# **Translation Control**

Address translation is controlled by a bit in the PSW as described in this section.

Additionally, the execution of the INVALIDATE PAGE TABLE ENTRY instruction is controlled by the translation format, bits 8-12 of control register 0. The definition of the translation format is the same as provided in ESA/390.

Additional controls are provided as described in <u>Chapter 5</u>, "Program Execution," on page 21. These additional controls determine whether the contents of each access register can be used to designate an address space.

### **Translation Modes**

The PSW bit that controls address translation is bit 17, the address-space-control bit. When bit 17 is zero, the CPU is in the primary-space mode. When bit 17 is one, the CPU is in the access-register mode. The handling of addresses in these two modes is summarized in Table 1 on page 12.

| Table 1. Translation Modes |                      |                       |                                |

|----------------------------|----------------------|-----------------------|--------------------------------|

| PSW Bit                    | Mode                 | Handling of Addresses |                                |

| 17                         |                      | Instruction Addresses | Logical <sup>1</sup> Addresses |

| 0                          | Primary-space mode   | Host-primary real     | Host-primary real              |

| 1                          | Access-register mode | Host-primary real     | AR-specified real              |

| Explanation:               |                      |                       |                                |

1

Certain real addresses are also handled differently according to the address-space-control mode. These real addresses are explicitly specified elsewhere in this publication.

# **Address Summary**

## **Addresses Translated**

Most addresses that are explicitly specified by the program and are used by the CPU to refer to storage operands are logical addresses and are subject to implicit translation by means of host access-register translation when the CPU is in the access-register mode. Analogously, the addresses indicated to the program as the result of executing an instruction are logical.

The addresses used by the CPU for fetching of instructions are instruction addresses and are hostprimary real addresses. Similarly, the instruction addresses indicated to the program on an interruption are host-primary real addresses.

Translation is not applied to quantities that are formed from the values specified in the B and D fields of an instruction byte that are not used to address storage. This includes operand addresses in LOAD ADDRESS, LOAD ADDRESS EXTENDED, MONITOR CALL, and the shifting instructions. This also includes the addresses in control registers 10 and 11 designating the starting and ending locations for PER.

With the exception of TEST PROTECTION, addresses explicitly designating storage keys (operand addresses in SET STORAGE KEY EXTENDED, INSERT STORAGE KEY EXTENDED, and RESET REFERENCE BIT EXTENDED) are real addresses that are resolved according to the translation mode. These addresses are considered host-primary real addresses when in the primary-space mode, and AR-specified real addresses when in the access-register mode. Similarly, the address of the storage operand for TEST BLOCK is a real address that is resolved according to the addressing mode.

The addresses implicitly used by the CPU for such sequences as interruptions are host-primary real addresses.

The addresses used by channel programs to transfer data and to refer to CCWs or IDAWs are hostprimary absolute addresses.

The handling of storage addresses associated with DIAGNOSE is dependent on the particular DIAGNOSE code. See *z/VM: CP Programming Services* for more information.

#### **Handling of Addresses**

The handling of addresses in ESA/XC is summarized in Figure 1 on page 14. This figure lists all addresses that are encountered by the program and specifies the address type.

#### **Instruction Addresses**

- Instruction address in PSW

- Branch address

- Target of EXECUTE

- Address stored in the word at real location 152 on a program interruption for PER

- Address placed in general register by BRANCH AND LINK, BRANCH AND SAVE, BRANCH AND SAVE AND SET MODE, BRANCH AND STACK, and BRANCH RELATIVE AND SAVE

Logical Addresses

- · Addresses of storage operands for instructions not otherwise specified

- Address placed in general register 1 by EDIT AND MARK and TRANSLATE AND TEST

- Addresses in general registers updated by MOVE LONG, MOVE LONG EXTENDED, COMPARE LOGICAL LONG, and COMPARE LOGICAL LONG EXTENDED

- Addresses in general registers updated by CHECKSUM COMPARE AND FORM CODEWORD, and UPDATE TREE

- Address for TEST PENDING INTERRUPTION when the second-operand address is nonzero

- Addresses for parameter list of RESUME PROGRAM

Real Addresses Resolved According to the Translation Mode

- Address of storage key for INSERT STORAGE KEY EXTENDED, RESET REFERENCE BIT EXTENDED, and SET STORAGE KEY EXTENDED

- Address of storage operand for TEST BLOCK

Host-Primary Real Addresses

- Storage operand of INVALIDATE PAGE TABLE ENTRY, LOAD USING REAL ADDRESS, and STORE USING REAL ADDRESS

- Trace-entry address in control register 12

- Dispatchable-unit-control-table origin in control register 2 (used by BRANCH AND SET AUTHORITY)

Permanently Assigned Host-Primary Real Addresses

- Address of the doubleword into which TEST PENDING INTERRUPTION stores when the second-operand address is zero

- Addresses of PSWs, interruption codes, and the associated information used during interruption

- Addresses used for machine-check logout and save areas

Absolute Addresses

• Failing-storage address stored in the word at real location 248

Figure 1. Handling of Addresses (Part 1 of 2)

Host-Primary Absolute Addresses

- Prefix value

- Channel-program address in ORB

- Data address in CCW

- · IDAW address in a CCW specifying indirect data addressing

- CCW address in a CCW specifying transfer in channel

- Data address in IDAW

- Measurement-block origin specified in SET CHANNEL MONITOR

- Address limit specified in SET ADDRESS LIMIT

- · Addresses used by the store-status-at-address SIGNAL PROCESSOR order

- CCW address in SCSW

Permanently Assigned Host-Primary Absolute Addresses

- Addresses used for the store-status function

- · Addresses of PSW and first two CCWs used for initial program loading

Addresses Not Used to Reference Storage

- PER starting address in control register 10

- PER ending address in control register 11

- · Address stored in the word at real location 156 for a monitor event

- Address in shift instructions and other instructions specified not to use the address to reference storage

Figure 2. Handling of Addresses (Part 2 of 2)

# **Assigned Storage Locations**

All of the storage locations assigned in ESA/390 are also assigned for the same purpose in ESA/XC, except as specified in the following. All assigned storage locations reside within the host-primary address space.

#### 144-147

(Real Address)

*Translation-Exception Identification*: During a program interruption due to a protection exception, if the suppression-on-protection facility is installed, information is stored at locations 144-147 describing the exception, as discussed in <u>"Suppression on Protection" on page 11</u>. Bit 29 being one indicates that the unit of operation or instruction execution during which the exception was recognized was suppressed, except that, if the instruction execution would set the condition code if completed normally, the condition code is unpredictable. Bit 29 being zero indicates that the operation was either suppressed or terminated. If bit 29 is set to one, bit positions 1-19 contain bits 1-19 of the effective address that caused the exception. The effective address is the address which exists before any transformation by prefixing. Bit positions 30-31 of real locations 144-147 are set to identify the address space containing the protected address, as follows:

#### 00

A type-R real address was used.

01

CPU was in the access-register mode, and either the access was an instruction fetch or it was a storage-operand reference that used an AR-specified real address. The exception access id, real

location 160, can be examined to determine the address space containing the address. However, if a type-R real address was used, bits 30 and 31 may be set to 00 instead.

Bits 0 and 20-28 of real address 144-147 are unpredictable.

#### 160

#### (Real Address)

*Exception Access Identification*: During a program interruption due to an ALEN-translation or addressing-capability exception, if the ALET being translated was obtained from an access register, the number of the access register used is stored in bit positions 4-7 of location 160, and zeros are stored in bit positions 0-3. If the ALET being translated was not obtained from an access register, then zeros are stored at location 160.

During a program interruption due to a protection exception, an indication of the address space to which the exception applies may be stored at location 160 if the suppression-on-protection facility is installed and bit 29 of the translation-exception identification is set to one. If the CPU was in the access-register mode and the access was an instruction fetch, including a fetch of the target of an EXECUTE instruction, zeros are stored at location 160. If the CPU was in the access-register mode and the access was a storage-operand reference to an AR-specified real address, the number of the access register used is stored in bit positions 4-7 of location 160, and zeros are stored in bit positions 0-3. If the CPU was not in the access-register mode, the contents of location 160 are unpredictable.

#### 168-171

#### (Real Address)

*Exception ALET*: During a program interruption due to an ALEN-translation or addressing-capability exception, the ALET being translated is stored at locations 168-171.

#### 256-263

#### (Real Address)

*Failing-Storage ASIT*: During a machine-check interruption, a failing-storage ASIT may be stored at locations 256-263. A failing-storage ASIT is stored whenever a failing-storage address is stored at locations 248-251.

# **Chapter 4. Control**

This chapter describes how the facilities for controlling, measuring and recording the operation of one or more CPUs for ESA/XC differ from those defined in ESA/390. Except as described in the following, the definition for control facilities provided in Chapter 4 of *IBM Enterprise Systems Architecture/390 Principles of Operation* applies to ESA/XC as well.

# **Program-Status Word**

The program-status word (PSW) is the same as defined in ESA/390, except as described in the following section.

## **Program-Status-Word Format**

| <br> 0 R 0 0 0<br>+-+-+  | I E <br>0 0 X  Key<br>+-+-+ | -+-+++++++++++<br>  1   0   0   0   0   0   0   0   0   0 | A    Prog<br>5  CC   Mask |    | 0 0 0 |

|--------------------------|-----------------------------|-----------------------------------------------------------|---------------------------|----|-------|

| 0 1 2                    | 5078                        | 12 10                                                     | 10 20                     | 24 | 21    |

| +-+<br>   <br> A <br>+-+ |                             | Instruction                                               | Address                   |    | +     |

| 32 33                    |                             |                                                           |                           |    | 63    |

#### Figure 3. PSW Format

All PSW fields (that is, those bit positions that are not required to be zeros) have the same function as in ESA/390, with the exception of PSW bit 17.

#### Address-Space Control (AS)

Bit 17 controls the translation mode. When bit 17 is zero, the CPU is in the primary-space mode; all logical, real and absolute addresses are considered host-primary addresses. When bit 17 is one, the CPU is in the access-register mode; all logical and certain real and absolute addresses are considered AR-specified addresses that reside within the address space determined by host access-register translation.

In addition to those bit positions unassigned in ESA/390, bit positions 5 and 16 are also unassigned in ESA/XC. A specification exception is recognized when these bit positions do not contain zeros.

## **Control Registers**

Control registers and control-register fields are the same as defined in ESA/390, except as specified in the following.

In ESA/XC, all bit positions of control registers 1, 4, 5, 7, 13, and 15 are unassigned. In addition, bits 1, 2, and 5 of control register 0; bits 16-31 of control register 3; bits 0-15 of control register 8; bit 30 of control register 12; and bits 12-31 of control register 14 are unassigned. All of these unassigned control-register positions are initialized to zero.

The section <u>"Changes in Control-Register Assignments" on page 53</u> identifies the functions associated with these control registers and control-register fields in ESA/390.

## Tracing

Tracing as defined in ESA/390 applies in ESA/XC except that ASN tracing is not provided. The ASN-tracecontrol bit is not provided, and SET SECONDARY ASN, PROGRAM CALL, PROGRAM RETURN and PROGRAM TRANSFER trace entries are never formed.

# **Program-Event Recording**

The ESA/390 definition of program-event recording (both PER 1 and PER 2) applies in ESA/XC except as stated in this section.

The PER-2 means of restricting storage-alteration events to occurring only when the storage is within designated address spaces is not provided in ESA/XC. In ESA/XC, storage-alteration events are not restricted to particular address spaces.

With PER 2, bit 10 of control register 9 is not ignored when DAT is off. Instead, when bit 10 of control register 9 is one, it is unpredictable whether any storage-alteration events are indicated.

## Timing

The timing facilities include three facilities for measuring time: the TOD clock, the clock comparator, and the CPU timer. Except as described in this section, the operation of the timing facilities is as defined in ESA/390.

### **Time-of-Day Clock**

An ESA/XC configuration does not have a TOD clock distinct from the TOD clocks of other ESA/XC configurations. Instead, all ESA/XC configurations are provided with shared access to the TOD clock of the host processor. The shared host TOD clock cannot be altered by the virtual machine. However, if the extended-TOD-clock facility is installed, SET CLOCK PROGRAMMABLE FIELD may be used to set the TOD programmable register for the virtual CPU.

The TOD clock is always in the set state. The STORE CLOCK and STORE CLOCK EXTENDED instructions store the current value of the host processor TOD clock, and always set condition code 0. On a single host system, two executions of STORE CLOCK or STORE CLOCK EXTENDED, possibly on different CPUs of different ESA/XC virtual machines, always store different values.

The SET CLOCK instruction is not provided. An attempt to execute the instruction results in an operation exception.

The TOD-clock synchronization facility is not provided.

# **Externally Initiated Functions**

#### Resets

The five reset functions provided in ESA/390 are also provided in ESA/XC, and perform all of the functions defined in ESA/390. In addition, the subsystem reset function performs additional actions in ESA/XC, as defined in the following.

Subsystem reset provides a means for clearing floating interruption conditions as well as for invoking I/Osystem reset. It also provides a means for resetting elements of the ESA/XC environment that are controlled by the host on behalf of the virtual machine.

#### **Subsystem Reset**

Subsystem reset operates only on those elements in the configuration which are not CPUs. In addition to the actions defined in ESA/390, subsystem reset in ESA/XC also performs the following actions:

- 1. All entries in the host access list are set to the unused state.

- 2. Any address spaces created using the ADRSPACE CREATE host service are destroyed.

- 3. The host-primary address space, if in the shareable state, is placed in the private state and access permission granted to other virtual machines is rescinded.

- 4. Certain other host-controlled entities are reset.

**Programming Note:** A list of the subsystem-reset actions on host-controlled entities is provided in the description of the SYSTEM RESET command in the publication <u>z/VM: CP Commands and Utilities</u> Reference.

20 z/VM: z/VM 7.2 Enterprise Systems Architecture/Extended Configuration Principles of Operation

## **Chapter 5. Program Execution**

Program execution for ESA/XC proceeds as defined in Chapter 5 of the *IBM Enterprise Systems Architecture/390 Principles of Operation* except for references in that publication to facilities defined elsewhere in this publication as not applicable to ESA/XC and except for other differences described in this chapter.

#### **Authorization Mechanisms**